### ETUDE DES PROBLEMATIQUES D'INTEGRITE DES SIGNAUX, DE CEM ET DE FIABILITE DES COMPOSANTS ELECTRONIQUES

Moncef Kadi

### ▶ To cite this version:

Moncef Kadi. ETUDE DES PROBLEMATIQUES D'INTEGRITE DES SIGNAUX, DE CEM ET DE FIABILITE DES COMPOSANTS ELECTRONIQUES. Electronique. Université de Rouen Normandie, 2011. tel-02308022

### HAL Id: tel-02308022

https://normandie-univ.hal.science/tel-02308022

Submitted on 8 Oct 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Travaux scientifiques Présentés à

### L'UNIVERSITE DE ROUEN

pour obtenir le

### DIPLOME D'HABILITATION A DIRIGER DES RECHERCHES

Spécialité : Electronique (section 63)

par

### **Moncef KADI**

### ETUDE DES PROBLEMATIQUES D'INTEGRITE DES SIGNAUX, DE CEM ET DE FIABILITE DES COMPOSANTS ELECTRONIQUES

Soutenue le  $1^{er}$  Avril 2011 à 10h30 à l'ESIGELEC devant la commission d'examen :

| Philippe DESCAMPS  | Rapporteur  | Professeur à l'ENSI Caen                |

|--------------------|-------------|-----------------------------------------|

| Etienne SICARD     | Rapporteur  | Professeur à l'INSA de Toulouse         |

| Lionel PICHON      | Rapporteur  | Directeur de Recherche au LGEP          |

| Kaouther DAOUD     | Examinateur | Professeur à l'université de Rouen      |

| Fabien NDAGIJIMANA | Examinateur | Professeur à l'UJF Grenoble             |

| Belahcène MAZARI   | Examinateur | Professeur CESI de ROUEN                |

| Odile PICON        | Examinateur | Professeur à l'université PARIS-EST MLV |

## SOMMAIRE

| Intr     | odu            | ction Générale                                                                                         | 8    |

|----------|----------------|--------------------------------------------------------------------------------------------------------|------|

| Δct      | ivité          | s de recherche                                                                                         | 11   |

| ا.<br>ا. |                | terconnexions RF sans fil avec antennes intégrées et interférences                                     |      |

|          |                | magnétiques                                                                                            | . 11 |

|          | l.1.           | Introduction                                                                                           | . 11 |

|          | 1.2.           | Travaux réalisés et principaux résultats                                                               | . 12 |

|          | I.3.           | Rapports et publications liés aux travaux sur les interconnexions RF sans fil                          | . 18 |

| II.      | Re             | éalisation et calibrage de sondes pour les mesures en champ proche                                     | . 19 |

|          | II.1.          | Introduction                                                                                           | . 19 |

|          | II.2.          | Travaux réalisés et principaux résultats                                                               | . 19 |

|          | II.3.          | Rapports et publications liés aux travaux sur le champ proche                                          | . 25 |

| Ш        | . CI           | EM des composants éléctroniques – immunité conduite                                                    | . 26 |

|          | III.1.<br>(Con | Immunité conduite des circuits intégrés face à des perturbations continues (<br>itinuous-Wave)         |      |

|          | III.2.<br>ESD  | Immunité conduite des circuits intégrés face à des décharges électrostatique (ElectroStatic Discharge) |      |

|          | III.3.         | Rapports et publications liés aux travaux sur l'immunité conduite                                      | . 45 |

| IV       | . Fi           | abilité des composants sous stress électromagnétique                                                   | . 46 |

|          | IV.1.          | Banc de stress électromagnétique rayonné                                                               | . 47 |

|          | IV.2.          | Fiabilité des TBH Si-SiGe sous contraintes électromagnétiques rayonnées                                | . 48 |

|          | IV.3.          | Fiabilité des technologies GaN utilisées dans les applications radars                                  | . 56 |

|          | IV.4.<br>appl  | Fiabilité des composants à semiconducteurs larges bandes pour les ications haute température           | . 56 |

|          | IV.5.          | Rapports et publications liés aux travaux sur la fiabilité                                             | . 56 |

| Con      | clus           | ions générales et perspectives                                                                         | . 58 |

| Bib      | liogr          | aphie                                                                                                  | . 61 |

| Anr      | iexe           | 1. Curriculum vitae                                                                                    | . 67 |

| A        | 1.l.           | Etat civil et fonction actuelle                                                                        | . 67 |

| A1.II.   | Titres                                                             | 68 |

|----------|--------------------------------------------------------------------|----|

| A1.III.  | Parcours professionnel                                             | 68 |

| A1.IV.   | Activité d'encadrement des travaux de recherche                    | 69 |

| A1.IV    | .1. Encadrement de thèses                                          | 69 |

| A1.IV    | .2. Encadrement de stages de Masters 2                             | 70 |

| A1.IV    | .3. Encadrement de stages de fin d'études                          | 71 |

| A1.V.    | Responsabilités collectives et rayonnements                        | 71 |

| A1.V.    | 1. Participations aux montages de dossiers de projets de recherche | 71 |

| A1.V.    | 2. Participations à des jurys de thèses                            | 72 |

| Annexe 2 | 2. Liste des travaux et des publications                           | 74 |

| A2.I. I  | Mémoires                                                           | 74 |

| A2.II.   | Revues internationales avec comité de lecture                      | 75 |

| A2.III.  | Conférences internationales avec comité de lecture                 | 77 |

| A2.III.  | .1. Conférences IEEE                                               | 77 |

| A2.III.  | .2. Autres conférences                                             | 77 |

| A2.IV.   | Conférences nationales avec comité de lecture                      | 79 |

| A2.V.    | Tableau de synthèse du nombre de publications par an               | 81 |

| Annexe 3 | 3. Activités d'enseignement                                        | 82 |

| A3.I. F  | Présentation générale                                              | 82 |

| A3.II.   | Principales contributions                                          | 83 |

| A3.II.:  | 1. Au niveau de la formation initiale                              | 83 |

| A3.II.2  | 2. Au niveau de la formation continue                              | 85 |

| A3.III.  | Enseignements dispensés                                            | 85 |

| A3.III.  | .1. Enseignements à l'ENSERG (2001/2004)                           | 85 |

| A3.III.  | .2. Enseignements à l'ESIGELEC (depuis 2004)                       | 86 |

| A3.III.  | .3. Enseignements dans des Masters 2 recherches (depuis 2006)      | 88 |

| Δηηργο / | 1 Quelques nublications dans des revues internationales            | an |

# **INTRODUCTION GENERALE**

### **INTRODUCTION GENERALE**

Les circuits électroniques connaissent depuis plusieurs décennies d'importants progrès caractérisés par des miniaturisations accrues permettant d'atteindre de très hautes performances. Ces progrès ont touché aussi bien les circuits élémentaires (transistors) que les circuits intégrés. Ils ont été rendus possibles grace non seulement aux développements des techniques de lithographie mais aussi à de grands efforts de recherche autour des technologies du semi-conducteur. En plus des technologies classiques en Silicium (Si) et leurs variantes (SOI, SOS, ...) ainsi que les technologies en Arséniure de Galium (GaAs), nous trouvons depuis quelques années des technologies émergeantes, à large bande interdite, très bonnes candidates aux applications de l'électronique hyperfréquence (GaN) et l'électronique de puissance (GaN et SiC). Ces technologies permettent de supporter de très forts courants à des températures très élevées (~300°C).

Avec le développement de systèmes mécatroniques embarqués intégrant de plus en plus de modules (hyperfréquence, puissance, numérique, ...); les problématiques de l'intégrité des signaux, la compatibilité électromagnétique (CEM) et la fiabilité ont connu un accroissement d'intérêt dans différents domaines (microélectronique, automobile, aéronautique ...). Dés lors, plusieurs travaux de recherche permettant d'appréhender ces problématiques ont été lancés aux niveaux des laboratoires universitaires et industriels. Cet intérêt est dû principalement au fait que ces thématiques concourent toutes les trois au même objectif : composants et systèmes fonctionnels, fiables et robustes.

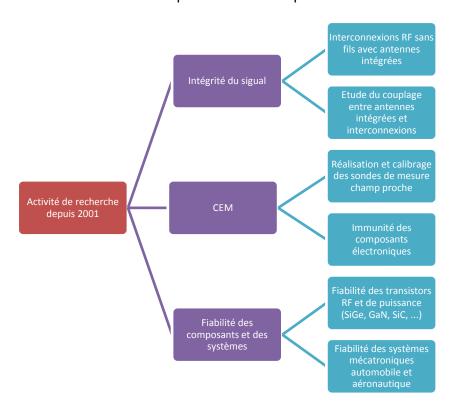

Je présente, dans ce rapport, un résumé de mes activités de recherche menées ces dix dernières années. Comme structuré sur la figure 1, ces activités sont directement liées au trois thématiques évoquées plus haut dans cette partie. Elles ont démarré avec une thèse de doctorat de l'université Joseph Fourrier, alors que j'étais rattaché au laboratoire IMEP (Institut de Microélectronique d'Electromagnétisme et Photonique). Cette thèse, dans le domaine de l'intégrité des signaux, portait sur l'étude d'interconnexions RF sans fil avec antennes intégrées. A la fin de cette thèse, j'ai rejoint l'IRSEEM/ESIGELEC en tant que Post-Doc pour devenir ensuite enseignant/chercheur dans le pôle Electronique & Systèmes (E&S). J'ai poursuivi une activité de recherche au sein de ce pôle, dans le domaine des antennes, plus particulièrement celles utilisées pour les mesures de champs proches en CEM. Je me

suis également intéressé aux effets des interférences électromagnétiques sur les circuits intégrés et les composants électroniques, une activité qui s'est articulée autour des thématiques : CEM et fiabilité des composants électroniques.

Figure 1 : Thèmes abordés dans mon activité de recherche.

## **ACTIVITES DE RECHERCHE**

### **ACTIVITES DE RECHERCHE**

# 1. Interconnexions RF sans fil avec antennes integrees et interferences electromagnetiques

#### I.1. Introduction

La course à la miniaturisation des circuits électroniques impose à l'industrie des semiconducteurs la fabrication de puces avec des densités d'intégration accrues. De plus, pour pouvoir aller de plus en plus vite, ces puces doivent travailler à des fréquences de plus en plus élevées. Face à ces deux contraintes, le réseau de lignes d'interconnexions se retrouve souvent pointé du doigt et semble être la principale source de limitation en termes de développement et de performances dans les nouvelles et futures générations de circuits intégrés. Parmi les solutions pressenties pour remplacer, pour certaines fonctions critiques, les lignes d'interconnexions classiques, nous trouvons les interconnexions optiques [Réf1], les interconnexions 3D [Réf2], [Réf3] et les interconnexions RF [Réf4]. Pour ces dernières, plusieurs travaux dans la littérature ont montré leur faisabilité pour des transmissions d'horloges intra-puces à des fréquences de 7,4 et 15 GHz [Réf4]-[Réf5], inter-puces à une fréquence de 15 GHz [Réf6] et sur PCB à une fréquence de 2 GHz [Réf7].

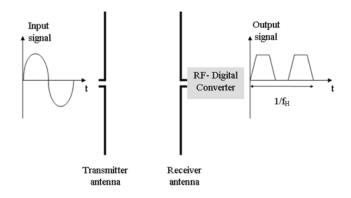

Figure 2 : Principe de la distribution d'horloge RF sans fil.

Le principe de cette transmission d'horloges est fondée sur le synoptique de la figure 2. Un signal mono-fréquence est transmis via une antenne d'émission vers une antenne de réception qui le récupère et le transfère à un détecteur pour restituer le signal d'horloge de

forme carrée. L'avantage de ce concept est d'utiliser un signal à bande étroite à l'émission contrairement à la méthode classique de distribution d'horloge qui utilise le signal carrée à plus large bande.

### I.2. Travaux réalisés et principaux résultats

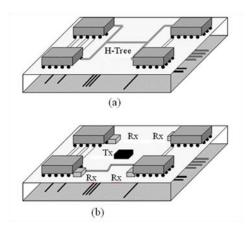

J'ai proposé dans mes travaux de thèse [T1] un nouveau concept d'interconnexions RF sans fil dédiées à la distribution d'horloge inter-puces sur « MultiChip Module ». Cette technique est prometteuse pour la distribution d'horloges dépassant le GHz sur des circuits de dimensions centimétriques. A ces fréquences, les dimensions centimétriques sont comparables aux longueurs d'ondes, ce qui complique considérablement l'utilisation des techniques classiques de distribution d'horloge. La solution proposée est une technique hybride qui repose sur l'utilisation d'antennes imprimées sur substrats high-K qui sont reportés ensuite sur le substrat du MCM utilisé (figure 3-b-).

Figure 3 : (a) Distribution classique d'horloge par arbre en H, (b) Illustration du concept de distribution d'horloge inter-puces sur MCM-L (Tx : antenne de transmission, Rx : antenne de réception).

Cette solution, telle que je l'ai développée, peut être appliquée aussi bien à des circuits MCM, qu'au niveau du PCB, pour la distribution d'horloges entre circuits intégrés. Elle remplacera principalement les circuits classiques de distribution d'horloges qui ont des formes d'arbres H équilibrés (figure 3-a-) et qui souffrent de la montée en fréquence des signaux d'horloges avec des temps de montée de plus en plus rapides. L'utilisation des matériaux high-K permet de réduire la taille de l'antenne d'émission et des antennes de réceptions. A l'instar du concept RF proposé sur la figure 2, cette solution nécessite

l'utilisation des circuits de réception qui se chargent d'amplifier et de restituer le signal d'horloge locale aux niveaux des puces. Ces circuits peuvent être facilement intégrés dans les puces, compte tenu des petites dimensions qui les caractérisent.

La réalisation des interconnexions RF sans fil nécessite la conception d'antennes de petites dimensions pour transmettre l'information par voie hertzienne d'un point à l'autre de la puce, entre puces ou entre plusieurs circuits. Dans les premières expériences présentées dans la littérature, les antennes utilisées étaient principalement des dipôles imprimés eu égard à la petite surface qu'ils occupaient contrairement à d'autres configurations planaires [Réf7]. Pour réduire leur taille, les dipôles n'étaient pas utilisés à leur longueur de résonance, ce qui rend leur impédance d'entrée complexe (partie imaginaire non nulle).

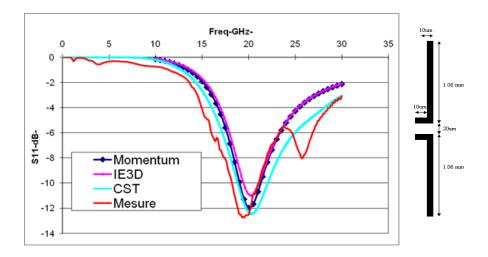

Les antennes proposées dans nos travaux [T1], [P10] sont aussi de forme dipôle imprimé. Elles sont réalisées sur deux types de substrats high-K : le LaAlO $_3$  et le MgO de permittivités respectives de 23,7 et 9. Sur la figure 4, nous présentons le coefficient de réflexion  $S_{11}$  du dipôle réalisé sur substrat LaAlO $_3$  de dimension  $5\times 5$  mm $^2$ , reporté sur de l'époxy de dimension  $5\times 5$  cm $^2$ . A la fréquence de travail qui est de 20 GHz, l'antenne a un  $S_{11}$  de -12 dB. Le dipôle a une longueur totale de 2,14 mm ( $\sim \lambda/2$  à 20 GHz) et une largeur de 20  $\mu$ m. Il a été réalisé en salle blanche en suivant les étapes technologiques habituelles de dépôt (par pulvérisation cathodique), de lithographie, de développement et de gravure.

Figure 4 : Coefficient de réflexion de l'antenne dipôle utilisée dans les interconnexions RF sans fil.

Ce premier résultat s'avère particulièrement important. Il montre clairement l'apport du substrat de haute permittivité, lequel a permis de réaliser une antenne adaptée (une bonne efficacité d'antenne), tout en gardant ses dimensions raisonnables. Pour le substrat MgO, le dipôle réalisé a une longueur totale de 3,15 mm et une largeur de 20 µm.

Dans la configuration du MCM-L étudiée, un des critères les plus importants pour la détermination de l'efficacité des interconnexions RF est le facteur de transmission de puissance entre antennes. La séparation entre antennes est de 1 ou 2 cm, en suposant que l'antenne d'émission soit placée au centre du MCM-L et que les antennes de réception soient placées autour; pour un circuit de dimensions de 5x5 cm² (figure 5-a- et figure 5-b-). Deux paramètres sont souvent calculés pour exprimer le bilan de puissance entre antennes. Le premier est le paramètre S<sub>21</sub> qui représente la racine carrée du rapport de la puissance reçue sur la puissance émise en tenant compte de la désadaptation des antennes d'entrée et de sortie. Le deuxième est le gain de transmission donné par la formule de Friis, qui exprime le rapport entre la puissance reçue et la puissance émise, pour le cas idéal où les antennes sont adaptées à l'entrée et à la sortie simultanément et où la transmission s'effectue par ondes sphériques.

Figure 5 : Différentes positions d'antennes pour les caractérisations en transmission (aantennes en face à face "Face to face", b- antennes en position décalée "Off set").

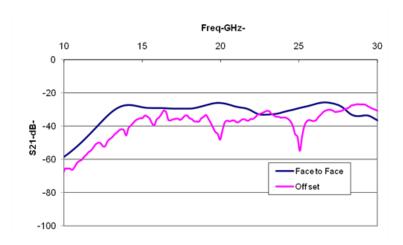

Sur la figure 6, nous présentons les résultats de mesures du coefficient de transmission  $S_{21}$  entre l'antenne d'émission et l'antenne de réception dans les deux configurations de la

figure 5. A la fréquence de 20 GHz, nous obtenons des niveaux de transmission de respectivement -20 dB et -50 dB pour les configurations "Face to Face" et "Off set".

Figure 6: Transmission entre deux dipôles en positions "Face to Face" et "Off set".

Afin de mesurer l'importance de ce résultat en le comparant avec les premières études de faisabilité sur les interconnexions RF sans fil, nous nous sommes intéressés au gain de transmission à deux fréquences particulières : 15 GHz et 20 GHz (tableau 1).

| Configurations | f     | S <sub>21</sub> | S <sub>11</sub> | S <sub>22</sub> | G     |

|----------------|-------|-----------------|-----------------|-----------------|-------|

|                | (GHz) | (dB)            | (dB)            | (dB)            | (dB)  |

| Face to face   | 15    | -35             | -5              | -5              | -31,7 |

|                | 20    | -20             | -12             | -12             | -19,5 |

| Off set        | 15    | -35             | -5              | -5              | -31,7 |

|                | 20    | -40             | -12             | 12              | -39,5 |

Tableau 1: Caractérisation de la transmission dans les interconnexions RF sans fil sur MCM.

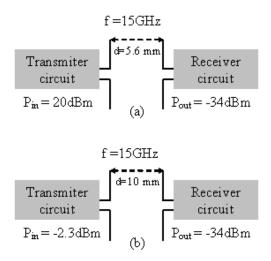

Dans ces deux configurations, la moins satisfaisante s'avère être la configuration "Off set" à la fréquence de 20 GHz avec un gain de -39,5 dB. Dans la littérature [Réf4], le meilleur résultat trouvé en transmission pour des interconnexions intra-puces est de -54 dB pour une séparation inférieure à 1 cm (figure 7). Ceci nous autorise à conclure à la faisabilité de notre solution. En effet, l'amélioration de la transmission entre antennes nous permet de diminuer au maximum la puissance délivrée au niveau de l'antenne d'émission. Ceci permet alors de réduire sensiblement l'effet des interférences électromagnétiques sur les interconnexions métalliques du circuit [P10].

Figure 7 : (a) Bilan de liaison dans la solution de Floyd et. al. [Réf4]. (b) Amélioration du bilan de liaison dans notre solution [P10].

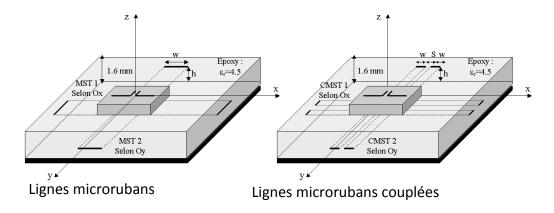

En effet, pour étudier ces interférences entre antenne d'émission et lignes d'interconnexions dans le MCM, nous utilisons le simulateur CST- Microwave studio. Le principe de la simulation consiste à exciter l'antenne d'émission et mesurer les paramètres S, exprimant le couplage entre l'antenne et les deux extrémités de la ligne (figure 8). Dans cette étude les lignes victimes sont des lignes microrubans enterrées (MST) et des lignes microrubans couplées (CMST). Elles ont une impédance caractéristique de  $50 \Omega$ .

Figure 8 : Structures des MCM considérées dans les simulations du couplage électromagnétique.

Les interférences entre antenne et lignes sont étudiées pour deux orientations principales de la ligne victime par rapport aux deux bras du dipôle :

• Le cas où les lignes sont parallèles aux bras de l'antenne, c'est le cas des lignes MST1 et CMST1 sur la figure 8.

Le cas où les lignes sont perpendiculaires aux bras du dipôle, c'est le cas des lignes

MST2 et CMST2 sur la figure 8.

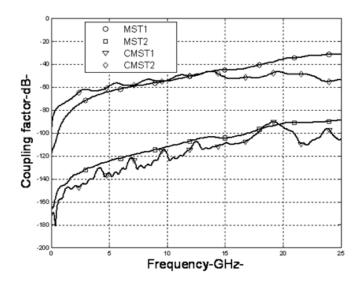

Nous remarquons, des résultats de la Figure 9, des effets différents selon la configuration et l'orientation de la ligne. Dans le cas de la ligne microruban, avec une orientation parallèle au dipôle le couplage est plus important que celui observé avec une orientation perpendiculaire (couplage quasiment nul) [P10]. Le couplage dans ce cas de figure est à prédominance magnétique. Dans le cas des lignes couplées, l'effet inverse est observé et le couplage est plutôt de type électrique [P10]. Ces résultats ont été obtenus pour des lignes enterrées juste en dessous du dipôle. Pour des lignes décalées, situées à la même hauteur, le couplage trouvé a été plus faible.

Figure 9 : Couplage entre antenne et lignes d'interconnexions enterrées.

Dans la majorité des configurations étudiées, le couplage parasite est resté de l'ordre de - 40 dB. Si nous considérons l'antenne d'émission excitée par une puissance de l'ordre de -10 dBm, nous nous retrouvons avec des puissances parasites dans les lignes victimes de l'ordre de -50 dBm ce qui correspond à des tensions induites de quelques millivolt pour des lignes  $50~\Omega$ . Ces niveaux restent suffisamment faibles pour provoquer des commutations parasites dans des circuits numériques ce qui est un autre point positif de la solution proposée.

## I.3. Rapports et publications liés aux travaux sur les interconnexions RF sans fil

| Rapports | Travaux en | Publications    | Conférences     | Conférences  |

|----------|------------|-----------------|-----------------|--------------|

|          | cours      | internationales | internationales | nationales   |

| [T1]     |            | [P10]           | [CI3], [CI12],  | [CN5], [CN6] |

|          |            |                 | [Cl13], [Cl14], |              |

|          |            |                 | [CI15], [CI18]  |              |

# II. REALISATION ET CALIBRAGE DE SONDES POUR LES MESURES EN CHAMP PROCHE

#### II.1. Introduction

Afin de caractériser les émissions électromagnétiques rayonnées par des circuits et des systèmes électroniques, l'IRSEEM a mis en place un banc de mesure champ proche basé sur la méthode directe [Réf9]. Dans cette méthode, les champs proches électromagnétiques peuvent être mesurés à l'aide d'un récepteur (analyseur de réseau ou un analyseur de spectre) et d'une petite antenne de réception appelée sonde. Cette dernière peut se déplacer au-dessus du dispositif sous test (DUT : Device Under Test) à l'aide d'un robot à trois axes cartésiens et à deux rotations [Réf10], [Réf11]. Les travaux présentés dans cette partie concernent la conception, la réalisation et le calibrage des sondes utilisées pour la mesure du champ électrique [Th1].

### II.2. Travaux réalisés et principaux résultats

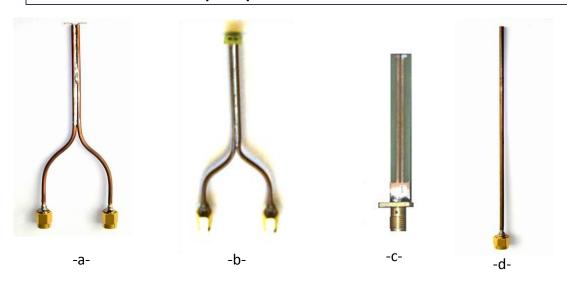

Figure 10 : Sondes électriques de types dipôles et monopole.

Les performances des bancs de mesure champ proche sont largement tributaires des performances des sondes utilisées. En effet, ces sondes doivent permettre de mesurer les vrais profils (critère qualitative) et les vrais niveaux (critère quantitative) des composantes du champ électromagnétique rayonné par le DUT. Dans le cas contraire, nous serons souvent amenés à développer des techniques de post traitement afin de corriger l'influence

de la sonde sur la mesure. Nous avons proposé, dans nos travaux, différentes configurations de sondes électriques : les dipôles filaires (figure 10-a-), les dipôles imprimés sur substrat diélectrique (figure 10-b-), les dipôles en technologie microruban (figure 10-c-) et les monopoles (figure 10-d-). D'autres sondes de types magnétique et mixte ont également été proposées dans ces travaux, mais ne seront pas présentées dans ce rapport [Th1].

### II.2.1. Caractéristiques des sondes de type dipôle électrique

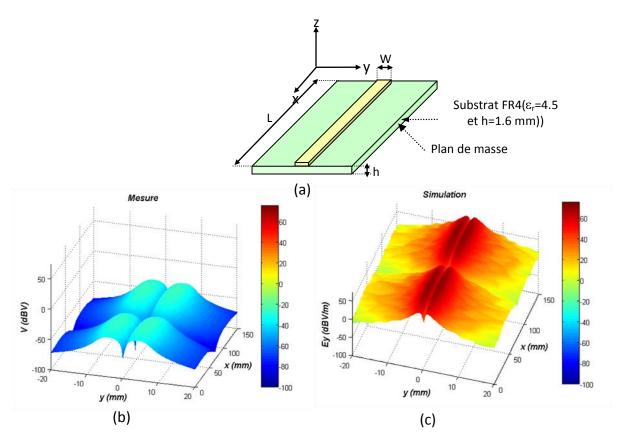

La longueur des dipôles doit être très inférieure à la longueur d'onde ( $L\sim\lambda/10$ ) afin d'une part de ne pas modifier l'environnement électromagnétique du DUT et, d'autre part de mesurer le vrai profil du champ rayonné. En effet, d'après la théorie des dipôles, nous savons que la tension induite par un champ électrique est le résultat d'une intégration du champ tangentiel tout le long des bras du dipôle. C'est cette intégration qui est responsable des décalages qu'on peut observer entre les profils mesuré et réel comme présenté sur la figure 11.

Figure 11 : Cartographies des champs électriques mesuré et simulé (réel) dans un plan situé à 1 mm au dessus d'une ligne microruban – sonde utilisée : dipôle linéaire de longueur 10 mm.

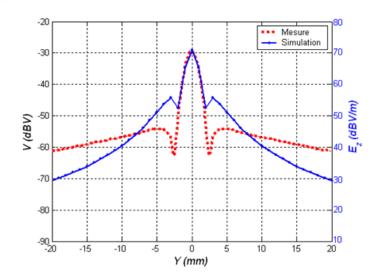

Sur cette même figure, nous pouvons constater en plus de la différence des profils, un décalage de niveau très important entre les deux cartographies. Ceci est principalement dû au facteur d'antenne de la sonde utilisée [P9], [Réf12]. Ce paramètre est le rapport entre le champ réel et la tension induite entre les deux brins du dipôle [Réf12]. Nous pouvons le calculer selon différentes méthodes et corriger ainsi l'erreur de niveau [P9]. En revanche, pour l'erreur de décalage de profils, nous sommes obligés de diminuer encore les dimensions de la sonde. Nos études ont montré qu'il est possible, pour ce type de sondes, d'avoir les mêmes profils pour une longueur totale (longueurs des brins + espacement entre brins) des dipôles  $\leq$  à 4 mm. Nous avons alors réalisé une sonde de longueur totale 4 mm et, comme nous pouvons le constater sur la figure 12, nous avons une très bonne concordance entre les champs mesuré et réel.

Figure 12 : Coupe du champ électrique à 1 mm au-dessus de la ligne microruban de la figure 11-a-.

Pour cette configuration de sondes, nous avons pu, en jouant sur la dimension, trouver la bonne sonde permettant d'éliminer l'erreur de profil. Dans certains cas, nous pouvons atteindre les limites technologiques de réalisation avant d'atteindre la miniaturisation souhaitée. Dans ce cas là, soit il faut changer de technologie (passage à une technologie planaire avec des substrats high-K par exemple), soit mettre en place des méthodes de post traitement bien adaptées afin de restituer les vrais profils de champs à partir des cartographies mesurées.

Par la suite, je développe la technique de post traitement que nous avons proposée dans le cas d'une sonde monopole.

#### II.2.2. Calibrage des sondes de type monopole

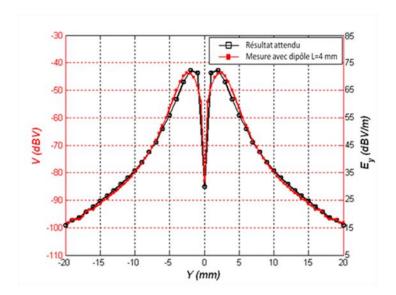

La sonde monopole utilisée est constituée d'un câble coaxial semi-rigide, lequel est coupé à ras d'un côté et connecté à un connecteur SMA de l'autre. Cette sonde permet la mesure des composantes normales du champ électrique  $E_z$ . Lors de son utilisation, nous étions confrontés aux mêmes limites évoquées précédemment. Sur la figure 13, nous pouvons remarquer la différence de profils et de niveau entre champ mesuré et champ simulé pour le même cas test évoqué précédemment.

La méthode de calibrage mise en place est fondée sur la décomposition en spectre d'ondes planes de la composante  $E_z$  du champ électrique [Réf13]. En effet, nous pouvons considérer que dans un plan parallèle au plan xy et situé à une hauteur z (le plan de mesure au dessus du DUT), le champ électrique pour chaque point appartenant à ce plan peut s'écrire comme une superposition d'ondes planes de mêmes fréquences et d'amplitudes différentes [Réf14]. Mathématiquement, ce concept s'exprime par l'équation (1). Cette équation peut également être généralisée au cas du champ magnétique [P7].

Figure 13 : Différence de profils et niveaux entre mesure et simulation de la composante normale du champ électrique au dessus d'une ligne microruban.

(1)

$$\vec{E}(x, y, z) = \frac{1}{4\pi^2} \int_{-\infty}^{+\infty} \vec{F}(k_x, k_y) e^{-jk_z z} \ \vec{e}^{-j(k_x x + k_y y)} dk_x dk_y$$

$\vec{F}(\vec{k})$  étant le spectre d'ondes planes et s'obtient par transformation inverse :

(2)

$$\vec{F}(k_x, k_y)e^{-jk_z z} = \int_{-\infty-\infty}^{+\infty+\infty} \vec{E}(x, y, z)e^{j(k_x x + k_y y)} dxdy$$

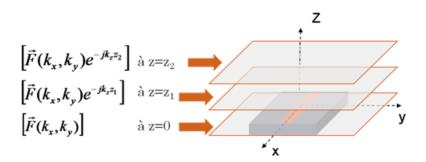

L'intérêt majeur de cette approche est la caractéristique de translation du spectre entre deux hauteurs différentes. En effet, si nous avons le spectre à un plan de référence, nous pouvons facilement l'obtenir à n'importe quel autre plan éloigné de z en multipliant par le terme  $e^{-jk_zz}$  (figure 14). Cette dernière propriété a été notamment exploitée pour la transformation champ proche/champ lointain dans le domaine des antennes [Mast4]. Nous avons démontré également son utilité en CEM et notamment le gain de temps qu'elle peut procurer en réduisant le nombre de plans et de composantes mesurés [P7].

Figure 14 : Propriété de translation du spectre d'ondes planes.

En pratique, si nous désignons par  $\vec{F}(k_x,k_y)e^{-jk_zz}$  le spectre du champ réel à une hauteur z au dessus du DUT, le champ mesuré par le banc champ proche peut se mettre sous la forme suivante :

(3)

$$\vec{E}(x, y, z) = \frac{1}{4\pi^2} \int_{-\infty}^{+\infty+\infty} \vec{F}(k_x, k_y) e^{-jk_z z} \cdot S(k_x, k_y) e^{-j(k_x x + k_y y)} dk_x dk_y$$

On introduit dans cette équation la fonction  $S(k_x, k_y)$  qui représente le spectre de la fonction de transfert de la sonde de mesure. La méthode mise en place pour l'extraction de cette fonction est basée sur l'utilisation d'un dispositif de référence rayonnant un champ théorique connu ou facilement simulable par un simulateur électromagnétique. Ce dispositif est ensuite mesuré à une hauteur donnée et ses deux spectres, théorique (ou simulé) et

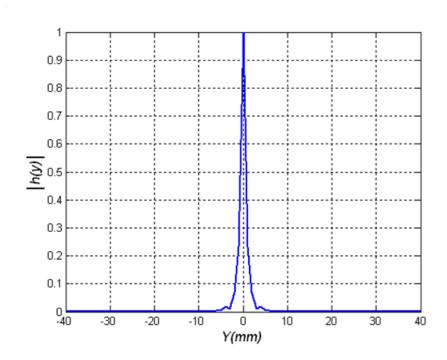

mesuré, sont calculés par une routine développée sous Matlab. En faisant le rapport du spectre mesuré par le spectre théorique (ou simulé), nous trouvons d'abord le spectre de la fonction de transfert de la sonde et ensuite, par transformation inverse, nous déterminons cette fonction dans le domaine spatial. Si on applique ce principe sur les données de la figure 13, nous trouvons la fonction de transfert de la sonde monopole qui est présentée sur la figure 15. Cette fonction est utilisée en post traitement des mesures champ proche d'autres dispositifs.

Figure 15: Fonction de transfert de la sonde monopole.

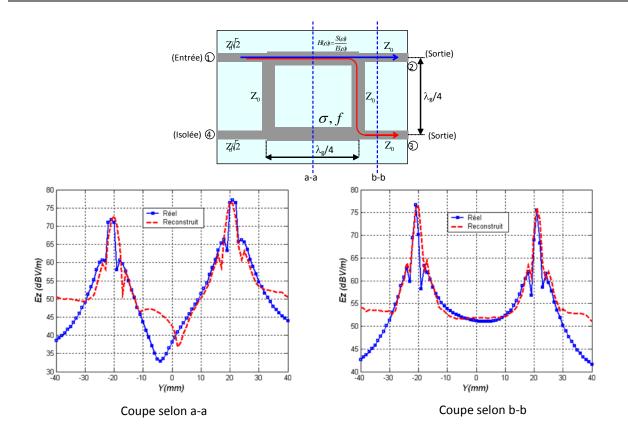

Elle permet ainsi de corriger les mesures faites avec la sonde monopole sur d'autres dispositifs. Sur la figure 16, nous montrons un exemple de cette correction appliquée au cas d'un coupleur hybride 90°. Une bonne concordance est observée pour deux coupes situées à deux endroits différents de l'hybride (a-a et b-b).

Nous avons appliqué cette technique de correction également au cas des sondes dipôles. Les résultats trouvés sont très satisfaisants et permettent facilement les corrections pour des cartographies et des coupes des champs électriques mesurés [P1].

Figure 16 : Correction des mesures de la composante normale du champ électrique rayonné par un hybride 90°.

### II.3. Rapports et publications liés aux travaux sur le champ proche

| Rapports                | Travaux en | Publications     | Conférences     | Conférences |

|-------------------------|------------|------------------|-----------------|-------------|

|                         | cours      | internationales  | internationales | nationales  |

| [Th1], [Mast4],<br>[S4] |            | [P1], [P7], [P9] |                 |             |

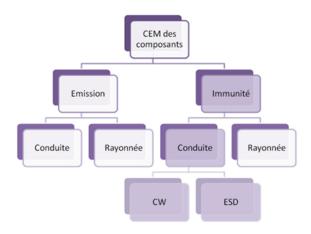

# III. CEM DES COMPOSANTS ELECTRONIQUES — IMMUNITE CONDUITE

La CEM des composants [Réf15] est l'une des trois thématiques couvertes par les activités du pôle E&S de l'IRSEEM. Cette thématique a été lancée en 2004 et a pour principal objectif de développer des modèles, CEM des composants, susceptibles d'être intégrés dans des platesformes de simulation. L'activité couvre les différents aspects de la CEM des composants électroniques qui peut se scinder en deux axes : l'émission et l'immunité (susceptibilité) (figure 17).

Figure 17 : Organigramme représentant les différentes branches de la CEM des composants.

Cette activité a démarré avec le programme de recherche intitulé « CEM des composants », lancé dans le cadre de la filière Haute Normandie AéroEspace et en partenariat avec Thales Air Systems. J'ai été chargé par le directeur de l'IRSEEM, M. B. MAZARI, du développement et du suivi de la thématique "Immunité Conduite", englobant aussi bien la partie CW (Continuous Wave) que la partie décharge électrostatique (ESD).

Comme évoqué précédemment dans ce document, les performances des circuits électroniques sont en constante évolution notamment en termes de fréquences de travail et de densité d'intégration. En plus de ces deux paramètres, une réduction des tensions d'alimentation est observée en passant d'une génération technologique à l'autre ce qui réduit sensiblement les marges de bruit de ces composants. Cela n'est pas sans conséquences sur l'immunité des composants électroniques face aux perturbations électromagnétiques de nature continue ou transitoire. Pour un intégrateur, la prise en

compte de ces phénomènes dès la phase de conception des circuits et systèmes électroniques, nécessite des modèles d'immunité fiables permettant des simulations CEM à l'échelle d'un circuit voire d'un système. Après le succès des modèles ICEM (IEC 62433-2 [Réf16] et IEC 62433-3 [Réf17]), dédiés aux émissions, tous les efforts dans le domaine de la CEM des composants sont centrés depuis quelques années sur les modèles d'immunité. C'est dans ce contexte que s'inscrivaient les travaux présentés dans cette partie. Ils sont divisés en deux parties :

- Immunité conduite face à des agressions de type CW.

- Immunité conduite face à des décharges électrostatiques ESD.

### III.1. Immunité conduite des circuits intégrés face à des perturbations continues CW (Continuous-Wave)

L'objectif principal de l'étude est la création d'un modèle d'immunité conduite précis et capable de décrire le comportement du circuit face à des perturbations électromagnétiques continues (CW). Ceci permettra de créer une bibliothèque de composants afin de réaliser des simulations globales et ainsi prédire l'immunité au niveau carte électronique ou même au niveau système, dés l'étape de conception.

La méthode de modélisation proposée dans nos travaux repose entièrement sur une caractérisation préalable de la susceptibilité de la broche sous test par application de la méthode DPI (Direct Power Injection) [Réf18]. Une attention particulière a été accordée dans ces travaux à la mise en place du banc de mesure DPI.

### III.1.1. Banc de caractérisation DPI de l'IRSEEM et ses spécificités

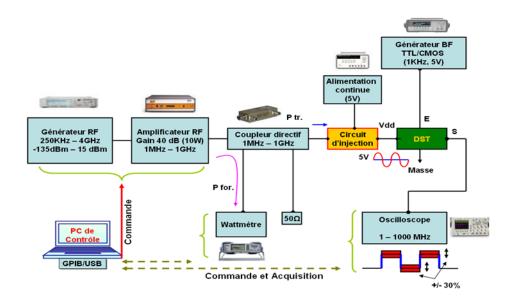

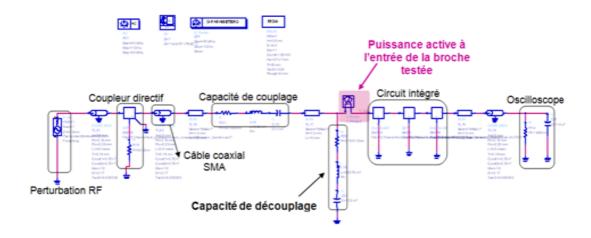

L'exactitude des mesures de susceptibilité est cruciale, notamment lorsque nous cherchons à construire un modèle de susceptibilité efficace qu'il soit fonctionnel ou comportemental. Pour cela, nous avons développé à l'IRSEEM un banc de mesure dont le principe repose entièrement sur la méthode d'injection directe de puissance (DPI) décrite dans la norme IEC 62132-4 [Réf18]. Les signaux RF générés sont notamment des signaux à onde entretenue ou CW. La figure 18 présente l'ensemble des appareils de mesure et de contrôle mis en œuvre lors des tests de susceptibilité conduite.

Figure 18: Synoptique du banc d'injection directe de l'IRSEEM/ESIGELEC.

Le banc de mesure peut être divisé en trois grandes parties. La première partie est la génération de la perturbation RF. Elle est constituée des équipements suivants :

- √ un générateur RF (250 KHz 4 GHz et Pmax=15 dBm).

- ✓ un amplificateur de puissance RF (Gain max=40 dB), 1 MHz−1 GHz, Pout max 10

W (un autre amplificateur de puissance maximale de 50 W a été souvent utilisé pour les circuits avec de fortes immunités conduites).

- ✓ un coupleur bi-directif (1 MHz 1 GHz, couplage de 40 dB sur les voies incidentes et réfléchies).

- ✓ un wattmètre (avec une sonde intégrée : -70 dBm 23 dBm).

- ✓ une alimentation DC.

- ✓ le prototype d'injection 1 MHz 1 GHz pour mélanger la composante continue au signal perturbateur RF (dans certains cas ce prototype est remplacé par un bias tee).

- ✓ les connecteurs ainsi que les câbles coaxiaux.

La seconde partie concerne la génération de signaux fonctionnels. L'objectif est de placer le dispositif sous test dans les mêmes conditions que celles qu'il peut rencontrer dans le cadre d'une application donnée. La troisième et dernière partie est liée au contrôle en temps réel

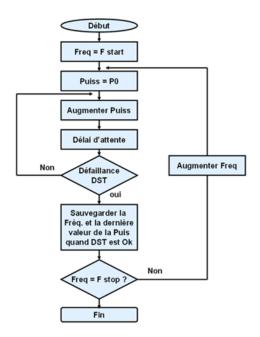

du comportement du circuit sous test. Elle est constituée d'un oscilloscope 4 voies large bande [1 MHz – 1 GHz] associé à une carte d'acquisition GPIB-USB. L'ensemble de ces équipements est contrôlé par un PC via un programme développé en labwindows CVI. Ce programme permet le pilotage de tous les appareils de mesure et applique des tests basés sur l'algorithme DPI représenté sur la figure 19.

Figure 19 : Algorithme DPI implanté dans le programme de pilotage du banc DPI.

Cet algorithme permet l'extraction de la courbe de susceptibilité de la broche du circuit soumise au test DPI. La défaillance du DST est observée en sortie via l'oscilloscope en fonction d'un critère basé sur la déviation de l'amplitude et de la phase du signal de sortie sans perturbation. Ce dernier est pris comme référence et un gabarit lui est appliqué spécifiant les tolérances en amplitude et en phase. Si sous une perturbation donnée, le signal de sortie sort de ce gabarit, le circuit a alors subi une défaillance. La courbe de susceptibilité consiste à relever pour chaque fréquence, la puissance de perturbation responsable de cette défaillance.

Tel que nous l'avons développé, le banc DPI de l'IRSSEM présente quelques spécificités. Les plus importantes sont les deux suivantes :

#### III.1.1.1. Correction de la courbe de réponse de l'oscilloscope

L'oscilloscope utilisé a une bande passante allant jusqu'à 1 GHz. A cette fréquence, il présente une atténuation d'environ 3 dB. Il en résulte que la réponse de l'oscilloscope n'est pas linéaire sur toute la bande DPI. Son influence est donc non négligeable sur la mesure. Pour cela nous avons caractérisé l'oscilloscope afin d'obtenir sa fonction de transfert. A partir de cette dernière, nous avons calculé une fonction correctrice qui n'est rien d'autre que l'inverse de cette fonction de transfert. Elle est implémentée dans le code et sert à corriger les mesures afin de s'affranchir de la réponse de l'oscilloscope.

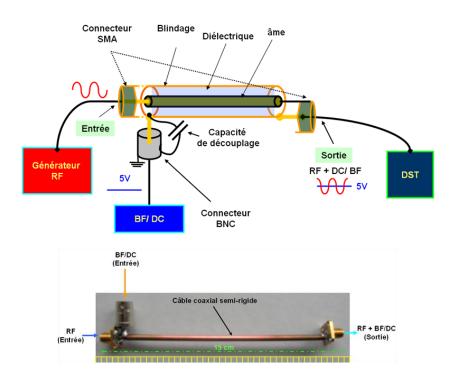

### III.1.1.2. Nouveau circuit d'injection

La deuxième spécificité du banc DPI de l'IRSEEM concerne le circuit d'injection présenté sur la figure 20.

Figure 20: Prototype et photo du circuit d'injection proposé pour le banc DPI de l'IRSEEM.

Dans la méthode DPI, nous utilisons classiquement une capacité d'injection d'une valeur comprise entre 1 et 10 nF pour coupler la perturbation à la broche sous test. Si l'agression est faite sur une broche d'alimentation par exemple, nous utilisons également des selfs de choc afin d'isoler la perturbation RF du signal DC. Le circuit d'injection que nous proposons sur le banc de l'IRSEEM est une sorte de "Bias Tee" réalisé à partir d'un simple câble coaxial

comme présenté sur la Figure 20. En effet, nous utilisons la transconductance du câble coaxial afin de séparer les composantes RF et DC. Ce circuit présente de faibles pertes sur toute la bande DPI (<à 1dB), ce qui assure sa complète transparence dans la chaine de mesure [P11].

#### III.1.2. Modèle d'immunité proposé basé sur les réseaux de neurones

Le modèle d'immunité que nous avons proposé est basé sur l'utilisation des réseaux de neurones afin d'extraire la fonction de transfert du circuit testé en présence de perturbations à l'entrée [P8]. La procédure de modélisation se déroule en 4 étapes :

- Expérimentations par application de la méthode DPI.

- Traitement et classification des données.

- Approximation par approche neuronale et extraction de la fonction mathématique.

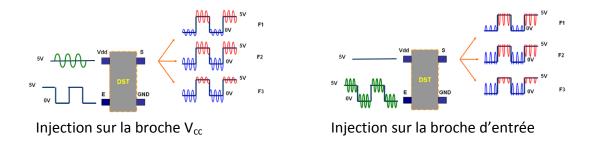

- Implémentation du modèle neuronal sous un logiciel de simulation type ADS.

La première étape repose principalement sur l'utilisation de la caractérisation DPI avec un algorithme légèrement modifié. En effet, au lieu de s'arrêter sur une puissance pour laquelle on provoque une défaillance selon un critère donnée, on fait toutes les puissances jusqu'à atteindre la puissance limite préconisée dans la méthode DPI. Ceci nous permet de recueillir un grand nombre de données et de pouvoir ainsi mieux modéliser notre composant. Pour chaque perturbation à l'entrée, l'amplitude de la perturbation en sortie est relevée à l'oscilloscope. Ces données sont ensuite classifiées dans des tableaux afin d'être utilisées dans la phase d'apprentissage. La structure du réseau de neurones utilisée est de type perceptron à trois couches : une d'entrée, une cachée et une de sortie. Nous avons validé cette approche dans le cas d'un inverseur CMOS à cinq broches, en modélisant la broche d'alimentation V<sub>cc</sub> et la broche d'entrée comme présenté sur la figure 21. Une fois les paramètres du réseau déterminés et la convergence atteinte, nous pouvons simuler la réponse du circuit à des perturbations CW de différentes fréquences et puissances.

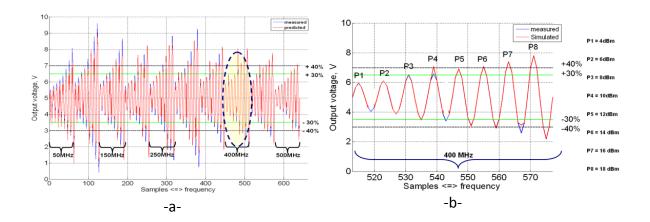

Figure 21 : Les deux configurations, de l'inverseur CMOS, utilisées pour la validation du modèle

Sur la Figure 22, nous présentons une comparaison entre les résultats de mesure et de simulation. Sur cette courbe, chaque période du signal de sortie correspond à la réponse du circuit à une puissance d'entrée donnée. Dans la représentation, nous avons simplement considéré une seule période du signal de sortie autour de l'état haut. Il convient de constater que les résultats du modèle sont en parfaite concordance avec les résultats de mesure.

Figure 22 : -a- Comparaison mesure et simulation autour du niveau logique haut sur la bande [50 - 500] MHz, -b- Zoom sur la fréquence de 400 MHz.

Ces premiers résultats montraient bien les performances du modèle neuronal proposé. Ce modèle est unique et présente un aspect innovant qui le démarque d'autres procédés de modélisation.

Cependant, pour ces premiers résultats, et afin d'assurer une bonne convergence, il nous a fallu utiliser plus de 1000 neurones par réseau. Ceci constitue une contrainte de taille quant à l'extraction de la fonction de transfert. Afin de remédier à cette limite, nous avons optimisé l'algorithme d'apprentissage pour répondre aux problèmes de sur-apprentissage et

sur-paramétrisation. Nous arrivons désormais à modéliser l'immunité conduite des circuits avec uniquement une vingtaine de neurones, tout en gardant les mêmes précisions [Th4],[CN1].

Ces travaux autour de l'optimisation du modèle neuronal, présenté dans la section précédente, ont été réalisés dans le cadre du projet EPEA et plus particulièrement dans le WP1 portant sur la création de modèles génériques de l'immunité des composants électroniques (cf. A1.V.1.3).

### III.1.3. Modèle d'immunité basé sur une approche paramètres [S]

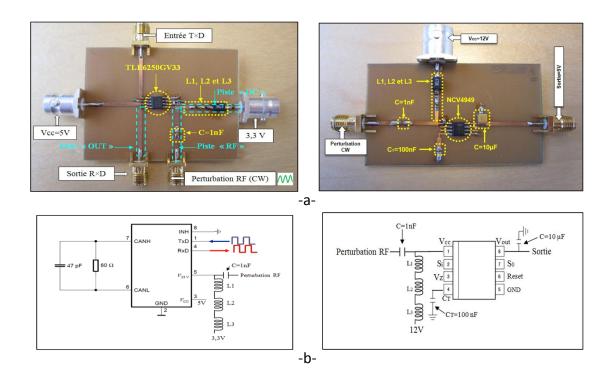

Nous nous sommes intéressés dans nos travaux de modélisation de l'immunité conduite à une deuxième approche, de type circuit, inspirée principalement des travaux présentés dans la littérature [Réf19]. L'approche a été testée dans le cadre du projet EPEA-WP1 sur deux circuits intégrés : le transceiver de bus CAN (TLE6250G) et le régulateur de tension (NCV4949). Les deux composants sont dans des boitiers SOIC de 8 broches. Des pieds de test adaptés aux essais DPI ont été réalisés (figure 23-a-) en mettant les deux circuits dans les configurations représentées sur la figure 23-b-.

Figure 23 : -a- Photos des pieds de test des circuits TLE6250G et NCV4949. -b- Câblage des deux circuits.

Pour réaliser les essais DPI, un "bias tee" a été rajouté sur la carte afin de découpler la polarisation DC des perturbations RF (figure 23). Ces dernières sont injectées sur les circuits à travers une capacité de 1 nF. Elles sont découplées du signal DC par trois inductances en série présentant une impédance totale supérieure à 1 k $\Omega$  sur toute la bande de fréquence des essais DPI [Réf19].

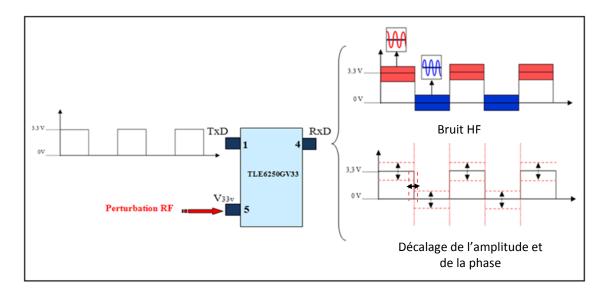

La deuxième méthode de modélisation que nous présentons dans cette partie est complémentaire à celle basée sur l'utilisation des réseaux de neurones présentée dans la partie précédente. En effet, quand un circuit subit une perturbation CW conduite, celle-ci agit sur la sortie de deux manières distinctes (figure 24):

- En se superposant sur les niveaux haut et bas des signaux numériques en sortie (bruit HF).

- En créant des variations des niveaux haut et bas et/ou en provoquant des phénomènes de jitter (décalage de phase) de ces signaux.

Figure 24 : Effet d'une perturbation RF sur la sortie d'un circuit intégré.

La complémentarité entre les deux méthodes de modélisation (neuronale et paramètres [S]) réside dans le fait que chacune modélise un des deux effets cités au-dessus. Ceci nous permet d'avoir une idée précise et surtout complète sur la réponse des circuits aux perturbations conduites.

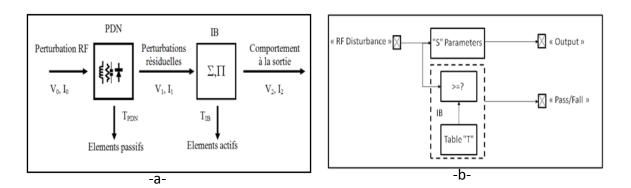

### III.1.3.1. Structure du modèle paramètres [S]

Plusieurs travaux, réalisés ces dernières années ([Réf20], [Réf21], [Réf22], [P8], [Réf23], [Réf24], [Réf25] et [Réf25]) ont contribué aux prémices d'un modèle d'immunité générique appelé ICIM-CI (Integrated Circuit Immunity Model — Conducted Immunity). Ce dernier est proposé par le groupe UTE (Union Technique de l'Electricité et de la Communication) pour une éventuelle standardisation [Réf26] à l'instar du modèle d'émission ICEM. La structure retenue pour ce modèle est présentée sur la figure 25-a-. Elle est composée d'un premier bloc appelé PDN (Passive Distribution Network) regroupant principalement les impédances du package, les fils de bonding et les interconnections intra-puce. Ce bloc est considéré comme un chemin de couplage intervenant comme des fonctions de filtrage et distorsion sur la perturbation RF. Quant au deuxième bloc de cette structure, il est appelé IB (Internal Behaviour) et représente la réponse fréquentielle "in band" et "out of band" du circuit intégré.

Le modèle paramètres [S], que nous avons proposé, remplace le bloc PDN par un seul bloc représenté par les paramètres [S] du circuit. Cependant, le comportement en immunité du circuit représenté par le bloc IB sera décrit par une table "T" représentant les puissances actives causant la défaillance du circuit en fonction de la fréquence (figure 25-b-).

L'utilisation du modèle est basée sur la comparaison dans une simulation de type circuit, de la puissance transmise au niveau de l'entrée avec la table "T" qui est extraite à partir des courbes de susceptibilité mesurées. En effet, en simulant sous ADS le modèle complet du banc DPI et de la carte de test nous pouvons aisément déduire les puissances actives "T" à partir des résultats de mesure des puissances incidentes (courbe de susceptibilité mesurée).

Figure 25 : -a- Synoptique du modèle ICIM-CI, -b- Synoptique et philosophie d'utilisation de notre modèle paramètres [S].

#### III.1.3.2. Extraction de la puissance active (transmise)

Après avoir modélisé chaque élément du banc DPI séparément, nous rassemblons les modèles élémentaires pour construire le modèle électrique global présenté sur la figure 26.

Figure 26 : Modèle global de la chaine de mesure et du circuit implémenté sous ADS.

La simulation de ce modèle permet d'extraire les valeurs de la puissance active à partir de celles de la puissance incidente obtenues par mesure DPI et lues au niveau du wattmètre. Cette puissance est déduite en utilisant l'équation suivante :

(4)

$$P_{active}=1/2\times(U^*.I+U.I^*)$$

Dans ce modèle global, le circuit intégré est représenté par trois boites. La boite centrale représentant les paramètres [S] mesurés entre l'entrée des perturbations RF et la sortie sur les cartes de la figure 23. Quant aux deux autres, elles sont utilisées pour réaliser un deembedding des paramètres [S] mesurés et ramener ainsi les plans de références au niveau du circuit intégré.

#### III.1.3.3. Validation du modèle

Pour valider le modèle composé des paramètres [S] et de la table "T" nous avons utilisé la procédure suivante :

Premièrement nous avons modélisé les circuits intégrés dans une configuration dite de référence sur laquelle nous n'avons pas câblé la capacité de découplage de la figure 26. Ce modèle est composé des paramètres [S] et de la table T. Cette dernière représente les puissances transmises causant la défaillance du circuit en fonction de la fréquence pour un critère de susceptibilité donné. Le critère retenu pour l'étude du régulateur de tension est la déviation de 30% des niveaux haut et/ou bas. Pour le transceiver de bus CAN il était plus difficile de définir le même critère avec des pourcentages donnés. Nous avons observé, une variation très importante à partir d'un certain niveau de puissance de la perturbation RF. C'est ce niveau qui a été retenu dans les courbes de susceptibilité.

Deuxièmement nous câblons plusieurs capacités de découplage afin de valider le modèle sur d'autres configurations différentes de la configuration de référence.

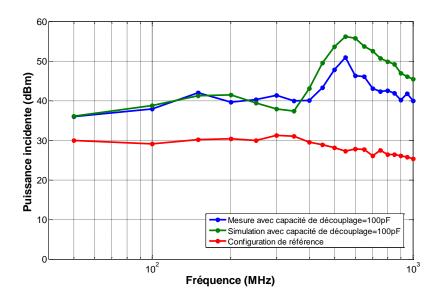

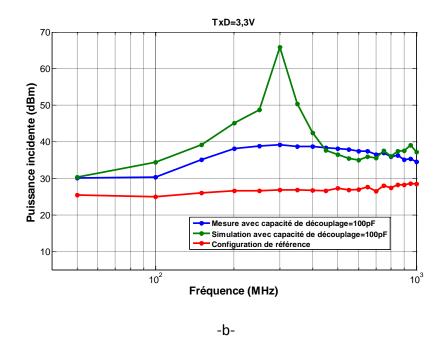

Sur la

figure 27, nous représentons les courbes de susceptibilité dans le cas des configurations de référence et avec capacité de découplage de valeur 100 pF. Pour cette dernière configuration, nous représentons la mesure et la simulation de la susceptibilité par le modèle. Nous remarquons une bonne concordance entre la prévision du modèle et la courbe mesurée. La même constatation a été faite pour la capacité de valeur 10 nF.

Figure 27 : Courbes de susceptibilité du NCV4949. Validation du modèle avec une capacité de découplage de 100 pF.

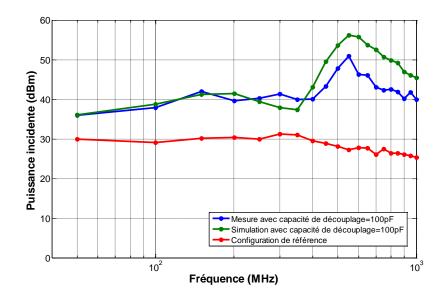

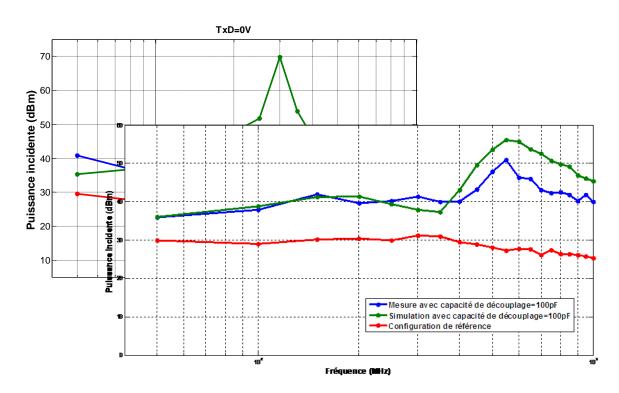

Dans le cas du TLE6250G, nous avons réalisé un modèle pour l'entrée TxD à 0 V et un modèle pour l'entrée TxD à 3,3 V. En effet, avec un signal carré à l'entrée il est difficile d'avoir des mesures stables des paramètres [S] d'où l'impossibilité de faire un seul modèle. Pour la configuration avec capacité de découplage de 100 pF nous avons comparé les courbes de susceptibilité mesurée et simulée sur la figure 28.

Figure 28 : Courbes de susceptibilité du TLE6250G. Validation du modèle avec une capacité de découplage de 100 pF : -a- TxD à 0 V, -b- TxD à 3,3 V (à droite).

Nous pouvons observer, sur cette figure, un bon accord entre la simulation et la mesure sauf autour de la fréquence de 300 MHz qui correspond à la fréquence de résonance de la capacité de 100 pF. A cette fréquence, nous nous somme limités en mesure à une puissance perturbatrice de 40 dBm, sans atteindre la défaillance fonctionnelle, pour ne pas endommager le composant. Ceci explique en partie l'écart considérable observé entre simulation et mesure. Par conséquent nous pouvons qualifier les tendances obtenues par le modèle de très correctes sur l'ensemble de la bande.

#### III.1.3.4. Interprétations des résultats obtenues

Les résultats obtenus avec la procédure de modélisation « paramètres [S] » sont très satisfaisants. Il ressort qu'ils sont beaucoup plus précis dans le cas du NCV4949 que dans le cas du TLE 6250G. En effet, cela peut s'expliquer par la réponse ESD des deux circuits qui est présentée dans la prochaine partie de ce rapport. IL apparait clairement que le phénomène "snapback" qui met en évidence le déclenchement des circuits de protection ESD et donc de phénomènes non linéaires est activé autour de tensions de 80 V pour le régulateur de tension et de 14 V pour le transceiver de bus CAN. Ceci peut expliquer les limites d'un modèle paramètre [S] (ne tenant pas compte des effets non linéaire) dans le cas d'un circuit

pour lequel les tests DPI contribuent à activer les non linéarités à travers les circuits de protection ESD.

## III.2. Immunité conduite des circuits intégrés face à des décharges électrostatiques ESD (ElectroStatic Discharge)

#### III.2.1. Introduction

Ce travail de recherche s'est réalisé en partenariat avec l'équipe électronique et CEM de VALEO. Il consistait à modéliser la réponse des circuits intégrés (ICs) face à des décharges électrostatiques (ESD). Le modèle devait être simple et facilement implémentable dans les outils de conception et de simulation électrique de type SPICE ou ADS. L'intérêt d'un tel modèle est double :

- Pour un concepteur de circuits et de cartes électroniques, il est de tenir compte des contraintes CEM, dès l'étape de conception, et réduire ainsi les temps et les coûts de développements de nouveaux produits.

- Pour les fabricants de circuits intégrés, l'intérêt est de dimensionner les circuits de protections ESD, implantés dans les circuits intégrés, en fonction de la réponse souhaitée [Réf27].

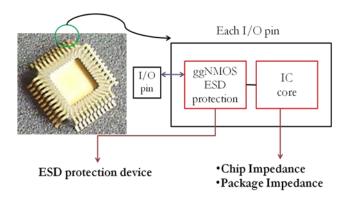

Le modèle que nous avons proposé est basé sur l'utilisation de composants standards pour modéliser le ggNMOS (grounded gate N-type MOSFET) qui est l'élément de base dans la protection ESD des circuits intégrés [Réf28]. Pour compléter le modèle proposé, le cœur du circuit intégré ainsi que son package sont modélisés par une impédance équivalente, à l'instar de ce qui est proposé dans le modèle ICEM (Integrated Circuit Emission Model). Le modèle est facile d'implémentation dans les outils de simulation électrique de type SPICE et permet d'effectuer des simulations rapides sans problèmes de convergence.

#### III.2.2. Structure du modèle proposé

Comme décrit précédemment, le modèle remplace le circuit sous test par un circuit de protection ESD associé à l'impédance équivalente du cœur et du package (figure 29).

Figure 29 : Structure simplifiée du modèle ESD d'un circuit intégré.

Dans notre modèle, l'organe de protection ESD est modélisé par trois composants :

- Un NMOS représenté par son modèle BSIM3V3.2 [Réf29],

- Un transistor bipolaire représenté par son modèle Mextram [Réf30],

- Une résistance de substrat R<sub>sub</sub>.

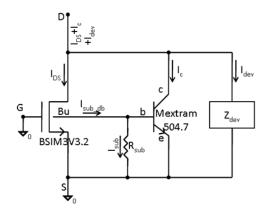

Sur la figure 30, nous présentons la disposition des différents éléments constituant le modèle. Le courant de substrat l<sub>sub</sub> est modélisé d'une part par le courant du substrat dans le modèle BISIM3V3.2 et d'autre part par le courant d'avalanche modélisé dans MEXTRAM. Ceci est une autre spécificité de notre modèle, lequel n'utilise aucune source de courant supplémentaire contrairement à d'autres présentés dans la littérature ([Réf31], [Réf32] et [Réf33]).

Figure 30 : Modèle SPICE pour simulations du phénomène ESD snapback.

#### III.2.3. Procédure d'extraction des paramètres du modèle

Pour extraire les différents paramètres constituant le modèle, une étape de caractérisation ESD est d'abord réalisée afin de mesurer la caractéristique I(V) de la broche testée. En effet, c'est cette caractéristique qui présente le phénomène de snapback à modéliser. Ce phénomène est représenté par une chute importante de la tension accompagnée d'une augmentation significative du courant à l'entrée de la broche. Ceci s'explique par l'activation du circuit de protection qui passe d'un état de blocage à un état de conduction ce qui augmente considérablement le courant le traversant.

#### III.2.3.1. Banc de mesure ESD

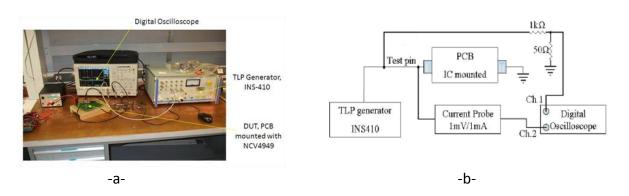

Les caractérisations ESD sont réalisées en utilisant le banc TLP (Transmission Line Pulsing) de la figure 31-a.

Figure 31 : a-Banc de caractérisation TLP de VALEO, b- Configuration de mesure de circuits intégrés.

Le générateur TLP utilisé est le INS410 de chez Noise Laboratories Co. Ltd. Il génère des impulsions avec un temps de montée fixe de 1 ns et une largeur réglable entre 50 ns et 400 ns par pas de 50 ns. Pour la mesure de la caractéristique I(V), le circuit sous test est monté sur un PCB et puis connecté au générateur TLP selon la configuration présentée sur la figure 31-b. Le courant entrant dans la broche sous test est prélevé par une sonde de courant 1mV/1mA.

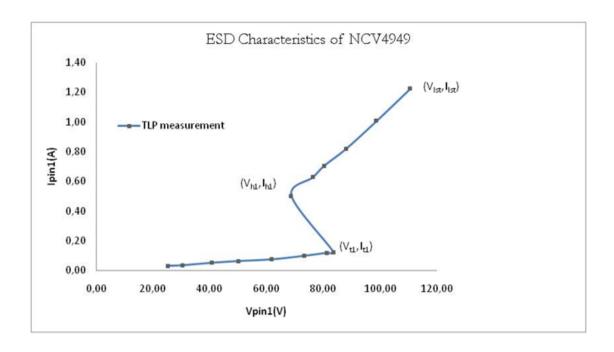

Sur la Figure 32, nous présentons le résultat de mesure de la caractéristique ESD du circuit intégré NCV4949.

Figure 32 : Caractéristique I(V) de la broche V<sub>cc</sub> du régulateur de tension NCV4949.

#### III.2.3.2. Mesure de l'impédance équivalente du circuit

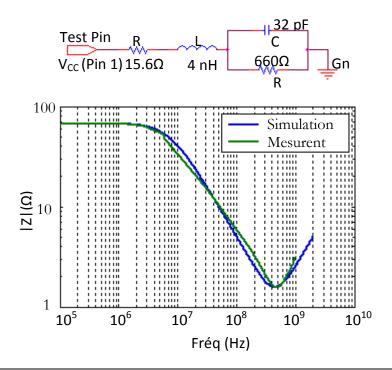

L'impédance équivalente du circuit est directement extraite de la mesure du paramètre  $S_{11}$  à l'entrée de la broche sous test. Cette impédance est ensuite modélisée par un circuit électrique équivalent à base d'éléments RLC. La figure 33 montre une comparaison entre une mesure d'impédance et son modèle électrique qui sera implanté dans le modèle final du circuit.

Figure 33 : Comparaison entre mesure et modèle de l'impédance de la broche  $V_{cc}$  du NCV4949.

#### III.2.3.3. Extraction des paramètres

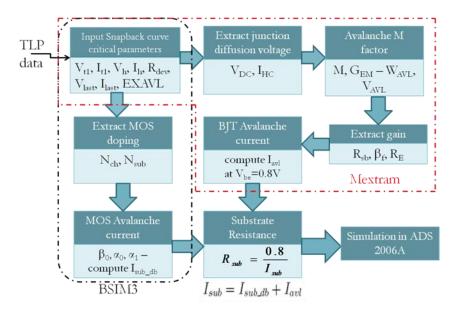

Certains paramètres de la caractéristique I(V) de la figure 32 seront directement exploités dans la procédure d'extraction automatique des différents paramètres des modèles des composants utilisés (le MOS et le bipolaire). Nous avons développé une procédure sous MATLAB afin d'extraire les principaux paramètres présentés dans le tableau 2 et le tableau 3 respectivement pour le BISIM3v3.2 et le MEXTRAM 504. La procédure mise en place est schématisée sur la figure 34.

| Parameter       | Description                                      | Units            |

|-----------------|--------------------------------------------------|------------------|

| $\alpha_0$      | The first parameter of impact ionization         | m/V              |

|                 | current.                                         |                  |

| $\alpha_1$      | $I_{\mathit{sub}}$ parameter for length scaling. | 1/V              |

| $\beta_0$       | The second parameter of impact                   | V                |

|                 | ionization current.                              |                  |

| W               | Device Width.                                    | m                |

| L               | Channel length.                                  | m                |

| DLC             | length offset fitting parameter.                 | m                |

| DWC             | Width offset fitting parameter.                  | m                |

| N <sub>ch</sub> | Doping concentration in the channel.             | cm <sup>-3</sup> |

Tableau 2 : Paramètres du BISM3v3.2 extraits par la procédure automatique.

| Parameter        | Description                               | Units |

|------------------|-------------------------------------------|-------|

| V <sub>AVL</sub> | Voltage determining the curvature of      | V     |

|                  | avalanche current.                        |       |

| W <sub>AVL</sub> | Epilayer thickness used in weak-          | m     |

|                  | avalanche model.                          |       |

| S <sub>fh</sub>  | Current spreading factor of avalanche.    | -     |

| $\beta_{f}$      | Ideal forward current gain.               | -     |

| R <sub>E</sub>   | Emitter resistance.                       | Ω     |

| I <sub>HC</sub>  | Critical current for velocity saturation. | Α     |

| R <sub>BC</sub>  | Constant part of the base resistance.     | Ω     |

| R <sub>BV</sub>  | Zero-bias value of the variable part of   | Ω     |

|                  | the base resistance.                      |       |

| $V_{DC}$         | Collector-base built-in voltage.          | V     |

Tableau 3 : Paramètres du MEXTRAM 504 extraits par la procédure automatique.

Figure 34 : Procédure d'extraction des paramètres du modèle ESD des circuits intégrés.

#### III.2.4. Validation du modèle proposé

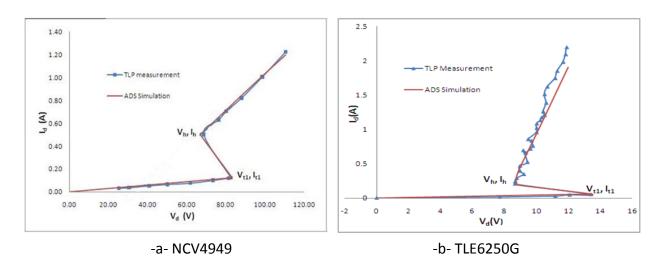

Le modèle proposé a été testé sur deux circuits intégrés différents : le régulateur de tension NCV4949 et le transceiver de bus CAN TLE6250G. Dans les deux cas, le modèle a donné de très bons résultats, comme le montre la figure 35. Les simulations ont été réalisées avec le logiciel ADS.

Figure 35 : Comparaison entre simulation et mesure TLP de la caractéristique ESD des circuits intégrés.

#### III.3. Rapports et publications liés aux travaux sur l'immunité conduite

| Rapports                                  | Travaux en | Publications                | Conférences                     | Conférences |

|-------------------------------------------|------------|-----------------------------|---------------------------------|-------------|

|                                           | cours      | internationales             | internationales                 | nationales  |

| [Th2], [Mast1],<br>[Mast2], [S2],<br>[S3] | [Th4]      | [P5], [P8], [P11],<br>[P12] | [CI6], [CI9],<br>[CI10], [CI11] | [CN1]       |

#### IV. FIABILITE DES COMPOSANTS SOUS STRESS ELECTROMAGNETIQUE

J'ai participé au démarrage de cette thématique de recherche au sein de l'IRSEEM au début de l'année 2007. Il s'agissait de mettre en place un partenariat entre le pôle E&S de l'IRSEEM et l'équipe de recherche en microélectronique (ERMEL) du GPM (Groupe Physique des Matériaux), unité de recherche mixte CNRS, université de Rouen et INSA de Rouen. La thématique retenue portait sur la fiabilité des composants électroniques sous stress électromagnétique. Cette collaboration a commencé par l'encadrement conjoint d'un stage de Master 2 recherche [Mast3] en partenariat avec Thales Air Système, désireux de qualifier la fiabilité et la robustesse d'une nouvelle technologie de composants susceptibles d'être utilisés dans les futurs développements de ses produits. Ce premier travail était une bonne étude de faisabilité et nous a encouragé à poursuivre les travaux par le lancement d'une thèse CARNOT ESP entre les deux laboratoires [Th3]. J'assure l'encadrement et le suivi de ces travaux conjointement avec Pr K. DAOUD du GPM, responsable de l'équipe ERMEL. Les travaux portent sur l'étude des dégradations et défaillances de composants Si-SiGe sous contraintes électromagnétiques.

Ces travaux mettent en synergie les compétences des deux laboratoires de recherche membres de l'institut carnot ESP. Du côté de l'IRSEEM, c'est les compétences en hyperfréquence et en compatibilité électromagnétique (CEM) qui sont directement exploitées dans cette thèse, pour mettre en place les bancs de stress électromagnétique rayonné, pour modéliser les composants sous tests et pour les caractériser avant et après stress. Du côté du GPM, c'est le savoir faire en analyse physique qui est mis à profit dans ce travail. En effet, une fois les composants dégradés, des analyses microscopiques sont réalisées afin de localiser les défauts et comprendre l'origine de la dégradation. L'implication des deux structures est très complémentaire surtout avec la pluridisciplinarité des domaines couverts par ces travaux.

En 2008, j'ai participé, côté IRSEEM, à la définition et au lancement du projet de recherche AUDACE "Analyse des caUses de DéfaillAnces des Composants des systèmes mEcatroniques embarqués". Ce programme est un projet de recherche et développement du pôle de compétitivité MOV'EO. Il regroupe quatorze partenaires industriels et universitaires et le

porteur du projet est THALES AIR SYSTEM. L'IRSEEM apporte dans ce projet son expertise en CEM (perturbations électromagnétiques), cette dernière étant identifiée comme l'une des principales sources de défaillances des composants des systèmes mécatroniques automobile et aéronautique. Ce projet est brièvement présenté dans l'annexe 1 (cf. A1.V.1.1).

#### IV.1. Banc de stress électromagnétique rayonné

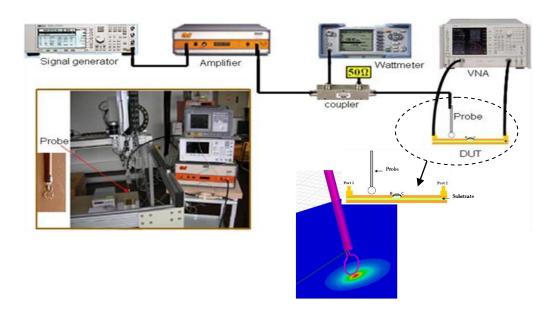

Le principe du banc de stress champ proche de l'IRSEEM présenté sur la figure 36 est fondé sur l'utilisation d'une sonde placée au-dessus du Composant Sous Test (CST) à une hauteur « h » pour injecter des perturbations rayonnées localisées de fortes amplitudes.

Figure 36 : Banc de stress électromagnétique rayonné.

Ce banc est constitué d'un générateur RF pour générer l'onde perturbatrice, d'un amplificateur pour l'amplifier, d'un coupleur et d'un wattmètre pour mesurer sa puissance et enfin d'une sonde d'injection pour la transformer du mode conduit en mode rayonné. Dans cette étude, la boucle magnétique a été retenue parmi les autres types de sonde comme le monopole et le dipôle. Cette sonde est fabriquée à partir d'un câble coaxial semirigide en prolongeant son conducteur central et en le formant en boucle pour produire principalement un champ magnétique perpendiculaire à sa surface.

#### IV.2. Fiabilité des TBH Si-SiGe sous contraintes électromagnétiques rayonnées

Le TBH étudié est un composant CMS (Composant monté en surface) de dimensions millimétriques monté en émetteur commun sur un pied de test constitué d'accès DC, permettant de fixer le point de polarisation et d'accès RF à travers des lignes 50  $\Omega$  [P4], [CN3]. Ces transistors présentent un gain en courant atteignant 300 et une tension de claquage BV<sub>CEO</sub> de 2,3 V.

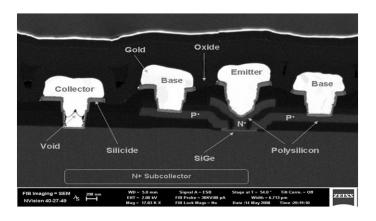

#### IV.2.1. Structure du composant Si-SiGe étudié

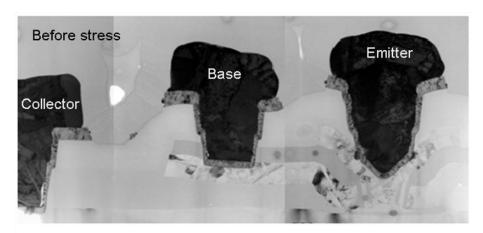

Afin de connaître la structure interne du TBH étudié, le composant a été dépackagé par procédé chimique. Ensuite, nous avons réalisé une ouverture d'une certaine profondeur par utilisation du FIB (Focused Ion Beam) afin d'inspecter la zone active du composant par le SEM (Scannig Electron Microscopy). A l'issue de ces procédés, nous avons pu remonter à la structure de notre TBH. Sur la figure 37, nous présentons une cellule élémentaire parmi six cellules constituant la structure multi-doigts du transistor. Nous identifions sur cette figure le collecteur, l'émetteur et la base avec une couche SiGe d'une épaisseur de 40 nm. Cette structure est utilisée comme référence du composant avant stress et sera comparée au cas des composants dégradés après stress.

Figure 37 : Une coupe du HBT Si-SiGe réalisée par le SEM.

#### IV.2.2. Dégradations des caractéristiques électriques des TBH après stress

Le stress électromagnétique est appliqué au TBH à travers une sonde située à 1 mm de hauteur et à 3 mm de la base. La puissance injectée dans la sonde est de 40 dBm à une

fréquence de 1 GHz. Après 2h30 de stress, nous avons remarqué une importante dégradation des caractéristiques statiques et dynamiques du transistor.

#### IV.2.2.1. Dégradations des caractéristiques statiques :

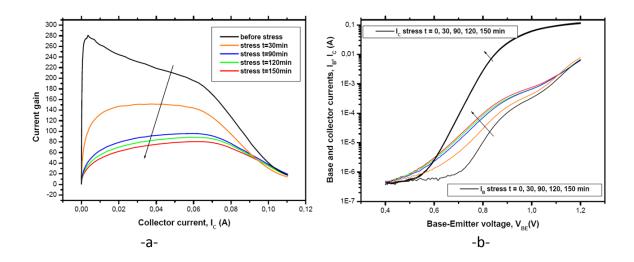

La Figure 38-a présente les courbes de Gummel avant et après stress avec  $V_{BE}$  qui varie entre 0,4 et 1,2 V à  $V_{BC}$ =0. Nous avons observé que le courant collecteur reste inchangé pendant la durée du stress, par contre une dégradation importante du courant de la base a été remarquée. Cette augmentation du courant de la base engendre naturellement une diminution du gain en courant du transistor comme nous pouvons le voir sur la figure 38-b.

Figure 38 : -a- Courbes de Gummel- $I_C$ ,  $I_B$  en fonction de  $V_{BE}$  à  $V_{BC}$ =0 V, -b- Gain du transistor en fonction du courant  $I_C$ .

Nous avons comparé cet effet sur les courbes de Gummel à l'effet des autres types de stress utilisés dans la littérature, notamment les deux stress électriques ("inverse" et "mixed mode") [Réf34], [Réf35] et celui par irradiation [Réf36]. Le mécanisme de défaillance commun responsable de cette augmentation du courant de la base est expliqué par des dégradations de la structure des couches d'isolation base-émetteur (espaceur), induisant un courant de fuite. En effet, la tension induite par stress électromagnétique à l'entrée du TBH augmente la vitesse des porteurs en induisant des porteurs chauds (électrons ou trous ou les deux). Ces très énergétiques introduisent des de porteurs centres Génération/Recombinaison (G/R) dans les couches d'isolation entre la base et l'émetteur en induisant un courant de base non-idéal et par conséquent une dégradation du gain en courant [Réf37].

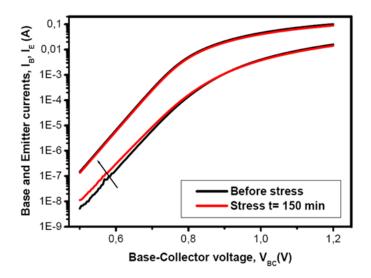

Afin de compléter nos investigations, nous avons mesuré également les courbes de Gummel en mode inverse (figure 39) qui représentent les paramètres associés à la diode Base-Collecteur du TBH. Nous avons remarqué une dégradation significative du courant de la base alors que le courant de l'émetteur reste inchangé. Par conséquent, une chute importante du gain en courant en régime inverse est induite. Ces résultats indiquent la présence d'un courant de fuite entre la base et le collecteur causé par les défauts à l'interface Si/SiO<sub>2</sub> des couches d'isolation base-collecteur [Réf38]-[Réf40]. Ceci montre que le stress électromagnétique induit des dégradations, non seulement à l'interface Si/SiO<sub>2</sub> entre la base et l'émetteur, mais aussi à celle de la couche d'isolation entre la base et le collecteur.

Figure 39 : Courbes de Gummel en mode inverse  $-I_E$ ,  $I_B$  en fonction de  $V_{CE}$  à  $V_{BE}$ =0 V.

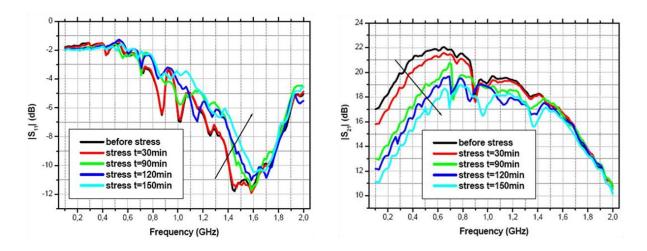

Les dégradations observées sur les caractéristiques statiques ont surement un effet sur les paramètres dynamiques du transistor. Pour mesurer l'importance de cet effet, nous avons caractérisé la dégradation des paramètres S pendant la durée du stress. De la figure 40, nous observons une importante dégradation du paramètre de transmission ( $S_{21}$ ) atteignant 5 dB. Ceci est attribué à la réduction de la transconductance ( $g_m$ ) due à la chute du gain statique en courant ( $\beta$ ) [Réf41]. En outre, il a été observé que le paramètre de réflexion ( $S_{11}$ ) a été dégradé (augmentation en module et en phase) après stress, ce qui indique une modification de l'impédance d'entrée du TBH. Cette dégradation peut être attribuée à

l'augmentation de la résistance dynamique de la base d'une part et à une modification des résistances de l'émetteur et de la base d'autre part.

Il est à signaler que ces dégradations étaient négligeables quand la sonde était placée au dessus du boîtier, du collecteur ou de l'émetteur en appliquant les mêmes conditions de stress.

Figure 40 : Dégradations des paramètres S après stress.

En plus de ces paramètres, nous avons observé la baisse de la fréquence de transition et l'augmentation des capacités de jonctions B-E et B-C. Pour le premier paramètre ceci est attribué à l'augmentation du temps de transite des porteurs à travers les jonctions B-E et B-C dégradées ainsi qu'à l'augmentation des capacités de ces jonctions. Quant à ces dernières, leur augmentation peut être attribuée en partie à l'augmentation de la concentration des porteurs aux niveaux des deux jonctions à cause du phénomène de piégeage cité précédemment.

#### IV.2.3. Analyse physique des défaillances

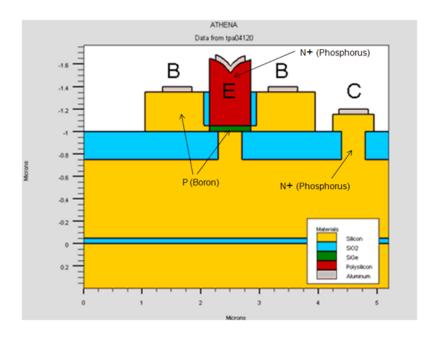

Afin de vérifier les hypothèses posées quant aux mécanismes de défaillances observés, nous avons eu recours à la simulation et à la caractérisation physique du TBH. Pour la simulation physique, nous avons utilisé les outils ATHENA — ATHLAS du logiciel SILVACO [Réf42]. Les études réalisées sur ces modules, nous ont permis de confirmer que le phénomène responsable de la dégradation du gain est principalement lié au phénomène de piégeage. Il est important de signaler que ces résultats sont à considérer d'un point de vue qualitative et pas quantitative. Ceci est dû d'un côté à la simulation d'une structure simplifiée différente

de la structure réelle (considération d'une seule cellule élémentaire au lieu de six) et de l'autre au fait que SILVACO est un logiciel 2D et donc considère uniquement une coupe de la structure réelle. La structure simulée sous ATHENA est représentée sur la figure 41. Les dimensions de cette structure ainsi que les dopages des différentes régions ont été optimisés afin d'avoir des caractéristique statiques proches de celles mesurées. Concernant le cœur du TBH, qui est sa couche SiGe, une épaisseur de 40 nm a été considérée conformément à ce qui a été trouvé par caractérisation physique (figure 37).

Figure 41 : Coupe bidimensionnelle de la structure du TBH SiGe simulé sous AHTENA.

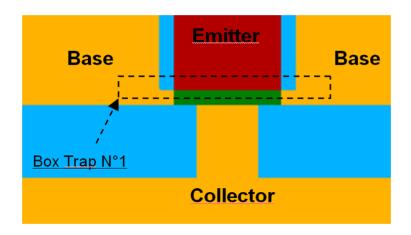

Les outils de simulation et de prédiction permettant d'évaluer la défaillance d'un composant électronique dans un environnement électromagnétique donné, ne sont pas disponibles à ce jour. Ceci nous a amené à introduire des défauts dans la structure pour comparer la variation des caractéristiques en simulation et en mesure, et pour pouvoir prédire la localisation des défauts après stress.

En effet, la cause la plus probable des dommages connus pour le TBH SiGe est la création d'états d'interfaces par des porteurs très énergétiques (porteurs chauds sous l'action d'un fort champ électrique), capables de casser les liaisons inter-atomiques fragiles de l'interface Si/SiO<sub>2</sub>. Par conséquent, le courant de recombinaison peut s'accroître à cause des pièges qui se trouvent à l'interface de ces couches d'isolations et qui font augmenter la vitesse de

recombinaison des porteurs en surface. Dans cette partie nous allons donc étudier par simulation l'effet des pièges sur les caractéristiques statiques et dynamiques.

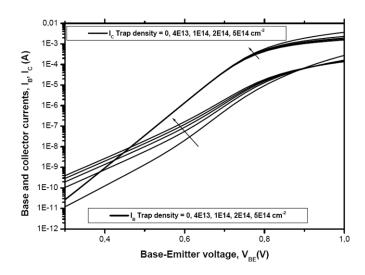

Le principe de la simulation consiste à introduire une densité de pièges aux interfaces Si/SiO<sub>2</sub> en utilisant la boite "Box Trap" comme représenté sur la figure 42. Selon le modèle utilisé des pièges, ces derniers s'appliquent seulement à l'interface Si/SiO<sub>2</sub> pour capturer les porteurs qui se déplacent à cette interface.

Figure 42 : Introduction des pièges à l'interface Si/SiO<sub>2</sub> entre la base et l'émetteur.

Nous avons observé par simulations l'effet de ces pièges sur les courbes de Gummel en mode direct avant et après introduction des pièges. Les résultats sont présentés sur la figure 43.

Figure 43 : Courbes de Gummel en régime direct simulées avec différentes densités de pièges.

De ces résultats, nous pouvons clairement remarquer que l'augmentation du courant de base est importante, et que le courant du collecteur n'a subi pratiquement aucun changement après introduction de défauts. Cette augmentation progressive du courant de base simulé est qualitativement comparable avec nos résultats expérimentaux. Ceci confirme l'hypothèse avançant l'apparition des pièges comme un des mécanismes de défaillance induit par le stress électromagnétique. Nous avons également remarqué le même effet sur les courbes de Gummel en mode inverse après avoir positionné des pièges aux interfaces Si/SiO<sub>2</sub> entre la base et le collecteur. Ces dégradations de caractéristiques statiques ont induit tout naturellement une baisse du gain en courant ainsi que le gain en puissance S<sub>21</sub>. Cependant, nous n'avons remarqué aucun effet sur le paramètre S<sub>11</sub> et donc l'impédance d'entrée contrairement à ce qui a été observé par mesures. Ceci est révélateur de la présence d'un autre type de défaillance en plus des pièges aux interfaces. Afin d'identifier ces défaillances supplémentaires, nous avons exploité les moyens de caractérisations physiques disponibles au laboratoire GPM.

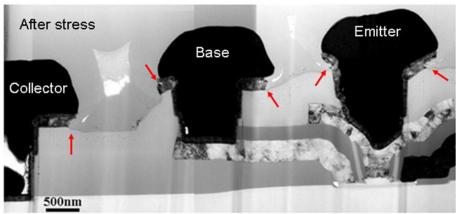

Sur la figure 44, nous comparons deux observations MET issues d'un composant vierge et d'un autre dégradé. Ce dernier est un composant vieilli pendant une durée de 2h30, où il a subi une dégradation du gain en courant de 80% après stress.

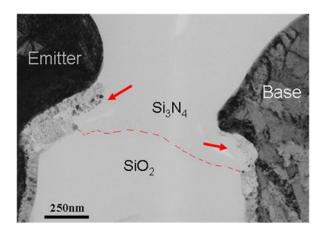

Sur la structure dégradée, nous pouvons remarquer une déformation de la couche de titane située sur les parties hautes des contacts de l'émetteur, de la base et du collecteur. La figure 45 montre clairement que la déformation du titane pour tous les doigts est limitée à l'interface Ti/Si<sub>3</sub>N<sub>4</sub>, s'arrêtant ainsi à l'interface Ti/SiO<sub>2</sub>.

Pour interpréter ces résultats des caractérisations EDS (Energy Dispersive Spectroscopy) ont été réalisés au niveau des zones dégradées. Il apparait clairement que des grains d'or ont migrés dans le titane pour former probablement des composés intermétalliques TiAu. Ce phénomène d'électromigration a pour origine le fort courant induit dans le transistor après stress. Ce courant provoque un phénomène d'auto-échauffement qui favorise l'électromigration de l'or.

Ces dégradations sont responsables de l'augmentation des résistances des contacts et ainsi l'impédance d'entrée du composant. Ce résulte complète l'analyse des causes de

défaillances et se trouve très complémentaire des simulations physiques présentées précédemment.

Figure 44 : Observation MET de deux structures dégradée et non-dégradée. Les flèches indiquent les dégradations observées dans les couches de titane.

Figure 45 : Observation MET en champ clair de la zone endommagée après stress. Les flèches indiquent les parties dégradées de la couche de titane, située autour des contacts de

l'émetteur et de la base. La ligne en pointillé est utilisée pour séparer les deux couches d'isolation  $SiO_2$  et  $Si_3N_4$ .

#### IV.3. Fiabilité des technologies GaN utilisées dans les applications radars

Avec le démarrage du projet AUDACE, j'ai poursuivi les travaux sur la fiabilité des composants électroniques sous stress électromagnétique. Nous nous sommes intéressés à la technologie GaN très bonne candidate aux applications de puissances mais pas toujours assez mature, ce qui représente un risque en termes de fiabilité et robustesse. La technologie GaN étudiée est utilisée dans les modules de transmissions radars pour réaliser les amplificateurs de puissance HPA (High Power Amplifier).

## IV.4. Fiabilité des composants à semiconducteurs larges bandes pour les applications haute température

Ces travaux ont démarré en octobre 2010 dans le cadre d'une collaboration entre les deux laboratoires GPM et IRSEEM. Ces derniers ont souhaité poursuivre naturellement leur travaux sur la fiabilité après la réussite de la première thèse [Th3] qui a mis en avant la parfaite complémentarité d'un point de vue thématique entre les deux laboratoires. Les travaux rentrent dans le cadre d'une thèse régionale et portent sur la fiabilité des composants à semiconducteurs larges bandes pour les applications haute température ([Th6]).

#### IV.5. Rapports et publications liés aux travaux sur la fiabilité

| Rapports       | Travaux en   | Publications      | Conférences         | Conférences  |

|----------------|--------------|-------------------|---------------------|--------------|